# ·测试、试验与仿真。

# Modelsim与MATLAB/Simulink联合仿真技术研究及应用

郭云飞,孙福海

(中北大学电子测试技术重点实验室,仪器科学与动态测试教育部重点实验室,山西 太原 030051)

摘 要:由于MATLAB/Simulink本身就是一款优秀的系统建模和算法仿真工具,Modelsim是国内最为常用的HDL仿真工具,利用Link for modelsim使 Modelsim与 Simulink 协同工作,使得算法设计和验证在同一款软件中完成。避免了不同开发环境下的兼容性问题,极大地简化了设计的复杂度,加快了开发进程。提出利用基于模型的设计方法,可以将算法与硬件实现联合起来,对于算法的开发以及后期硬件实现都会带来极大的方便。详细介绍了Modelsim与MATLAB/Simulink联合仿真的接口技术、模型的搭建,以及通过利用16 QAM调制与解调的应用实例来验证系统的正确性。

关键词: Modelsim; MATLAB/Simulink; 16 QAM调制与解调

中图分类号:TN709 文献标识码:A 文章编号:1673-1255(2013)-06-0091-06

# Research and Application of Modelsim and MATLAB/Simulink United Simulation Technology

GUO Yun-fei, SUN Fu-hai

(Education Ministry Key Laboratory of Instrumentation Science & Dynamic Measurement, Key Laboratory of Electronic Measurement Technology, North University of China, Taiyuan 030051, China)

**Abstract:** MATLAB/Simulink is a good system modeling and algorithm simulation tool and Modelsim is the most commonly used HDL simulation tool in China. Modelsim can cooperate with Simulink using Link for modelsim. And the algorithm design and validation are finished in the same software so that compatibility issues under different development environment are avoided, design complexity is simplified greatly and development process is advanced. The design method based on models is introduced. The algorithm with hardware can bring great convenience to algorithm development and subsequent hardware implementation. The interface technology and model building of Modelsim and MATLAB/Simulink united simulation are introduced. And the validity of the system is verified by the application example of 16 QAM modulation and demodulation.

Key words: Modelsim; MATLAB/Simulink; 16 QAM modulation and demodulation

随着系统规模和复杂度的提升,产品规范的制定难度成倍增加,缺陷问题日益突出。只有到了设计的后期缺陷才能被发现,工程师们急需一种能够支持系统开发的方法。

基于MATLAB平台的Simulink是动态系统仿真 领域中著名的仿真集成环境,它在众多领域得到广 泛应用。Simulink仿真库里提供的link for modelsim 功能,它提供了把 MATLAB / Simulink 和 FPGA 和 ASIC的硬件设计流程无缝连结起来的联合仿真接口 扩展模块,它的快速双向连结将 MATLAB/Simulink 和 硬件描述语言 Modelsim 连结起来,使二者之间直接 的联合仿真成为可能,并且更高效的在 MATLAB / Simulink 中验证 ModelSim 中的寄存器传输级(RTL) 模型。利用 Link for modelsim 使 Modelsim与 Simulink

协同工作降低了系统级开发的复杂度,提高对设计的验证效率<sup>[1]</sup>。该方法不仅应用于后期的验证,同时可以在开发初期进行。

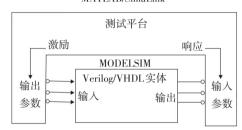

# 1 联合仿真系统搭建

Link for modelsim是一个联合仿真的接口,它将Mathwoks工具整合到EDA工作环境中,使其应用于FPGA和ASIC的开发。这个接口在HDL仿真器ModelSim SE/PE和MathWorks的产品MATLAB和SimuLink间提供了一个双向连接,以指导硬件的设计验证和联合仿真。这种整合可以分别充分发挥MATLAB/SimuLink和ModelSim各自的优势。图1显示了在MATLAB/SimuLink和ModelSim的接口关系。

MATLAB/SimuLink

图 1 MATLAB / SimuLink 和 Modelsim 的接口关系

首先,在MATLAB中产生仿真所需要的输入信号(信号加噪声),以十六进制的形式存放在数据文件中;其次,在ModelSim中用VHDL编写仿真测试文件(TestBench)<sup>[2]</sup>,用IEEE的TEXTIO库中的READ和RESDLINE函数将上述仿真数据文件中的测试向量读入,在ModelSim中做布局布线后的仿真(时序仿真),并调用WRITE和HWRITE函数将仿真结果写入另外一个数据文件中;最后,在MATLAB中将ModelSim仿真输出数据文件中的数据读入一个数组中,可以做图分析,或做进一步的误差分析。还可以将ModelSim中的仿真结果与MATLAB中做出的理论结果相比较来验证设计的正确性。这样可以比直接用人工方法将输入数据通过波形输入,再用人工方法通过对比输出波形中的数据来验证设计的正确性要直观、方便的多。

图 1 显示了在 MATLAB / SimuLink 和 ModelSim 的接口关系<sup>[3]</sup>。将产生的数据输入文件作为 ModelSim 的仿真输入向量,在 ModelSim 中做布局布线后的仿真,并将仿真的输出结果导入数据文件中,再用 MATLAB 做出其图形来。

#### 2 调制解调仿真/联合仿真的应用实例

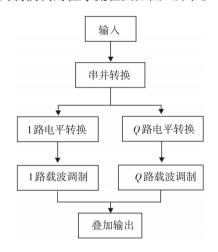

#### 2.1 16 QAM 调制的 FPGA 实现

16 QAM调制其功能是将基带信号分成两路分别映射成两路正交的载波振幅,然后将两路调制后的载波合成一路,在此过程中一共有两种数据速率。因此可以分为四个模块:正交载波产生模块DDS、调制模块16 QAM、时钟分频模块CLK\_DIV、顶层模块TOP QAM<sup>[4]</sup>。

DDS模块和时钟分频模块均采用 Xilinx 内部自带的IP核来生成<sup>[5]</sup>,IP核的利用大大简化了设计中编程的复杂度与加快了整个工作的进程。

调制模块的程序流程图如图2所示。

图2 调制流程图

输入为串行数据,需要经过串并转换<sup>[6]</sup>,最后将调制后的两路信号相加得到DATA\_OUT信号输出。映射调制的一个分支程序实现。

case(BUF\_IN2[1:0])

2'B01: begin

if (SIN\_WAVE==16'B0)

SIN\_OUT<=0;

else begin

SIN\_OUT[17]<=~SIN\_WAVE[15];

if (SIN\_WAVE[15])

$$\begin{split} & \text{SIN\_OUT[16:0]} <= & \{1 \text{ b0}, \sim \text{SIN\_WAVE[14:0]} + 1 \text{ 'B1}, 1 \text{ 'b0} \} + (\{2 \text{ 'b0}, \sim \text{SIN\_WAVE[14:0]} \} + 1 \text{ 'b1}); \end{split}$$

else

SIN\_OUT[16:0] <=~ ({1'b0,SIN\_WAVE[14:0],1'b0} + {2'b0, SIN\_WAVE[14:0]})+1'b1;

end;

end:

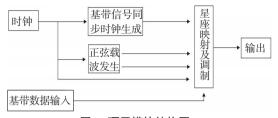

顶层模块主要实现各个模块的连接,以及参数的传递如图3所示。

图 3 顶层模块结构图

#### 2.2 16 QAM调制与解调的模型搭建

正交幅度调制采用4状态幅移键控对分别两路 正交载波进行调制,最后再将两路已调制信号合并 为一路信号输出。在接收端通过相干解调获得发送 端发送的两路信息,最后转变成一路二进制信息输 出。

16 QAM一般采用相干解调,根据星座映射图不同解调的实现略有差别<sup>[7]</sup>。解调的基本流程如下:将输入信号分别于两路正交的本地恢复载波相乘,然后经过低通滤波器之后,经过量化和并串转换即得到发送端发送的信息。

创建待仿真实体的 Simulink 模块[8]

- ①在 Matlab 中命令窗口中输入"edaCosimAssist" 执行即可开配置向导。

- ②选择执行联合仿真的软件。在该步骤中HDL cosimulation with可以选择 Matlab 或者 Simulink,选择这两种联合仿真工具时工作方式会有所不同,在这里选择 Simulink。在 HDL simulation 选项一栏可供选择的有 Modelsim 以及 candence、synplisys 公司的 HDL 仿真工具,选择 Modelsim。其他默认即可,设置如图 4所示。

图 4 选择联合仿真工具

③添加HDL文件,该步骤较为简单无特殊要求, 点击ADD按钮将相应的HDL文件添加进来即可,添 加完HDL程序后如图5所示。

④编译HDL文件,在该步骤需要注意的是Mod-

elsim可能无法正确处理 Verilog 中调用的原语,特别是一些 IP核生成的功能模型。

图5 添加HDL文件

Xilinx 大多数的 IP 都是不支持 Verilog 的,因此生成的 Verilog 模型是由网表文件反编译得到的,其中包含大量的原语,这些原语在联合仿真时 Modelsim 无法编译。因此生成 IP 核时应选择生成 VHDL 功能模型。

- ⑤利用Modelsim读取HDL模块的相关信息,获取端口信息。该步骤执行时间相对较长,会出现Dos窗口。

- ⑥端口类型设置。Simulink 通过 Modelsim 读取端口信息并对时钟和复位信号进行推测,在Simulink 与 Modelsim 的联合仿真中时钟和复位信号是在配置过程中设置相应时序,因此需要确保时钟和复位端口被正确设置。在步骤⑤中软件会推测相应的端口类型,所以大多数端口类型保持默认即可如图6所示。

图6 端口类型设置

⑦HDL程序端口数据类型的设置。由于Simulink不支持逻辑类型数据,因此HDL程序的端口需要设置为非逻辑类型。在这个过程中HDL程序的输出端口的数据类型是可配置的而输入端口类型是不可配置的,因此在HDL程序设计之初就必须将输入端口的数据类型成非逻辑类型。将输入端口的数据类型定义为非逻辑类型是可以通过语法检查的,但是不能综合即无法下载到FPGA中(因此联合仿真的程序是由实际程序修改了数据类型后得到的)。端口类型设置如图7所示。

- ⑧设置时钟周期和复位时间。在下一步中会以时序图的形式展示。

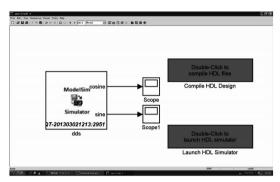

- ⑨生成Simulink模块,完成后的界面如图8所示。

图7 HDL程序端口数据类型设置

如图 8 所示, 在生成的 HDL 模块的输出端添加两个示波器即可完成简单联合仿真了。

图 8 Simulink 模块生成完成

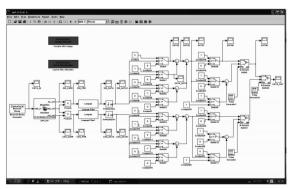

### 3 联合仿真

模型中信源采用Bernoulli Binary Generator,信号数据类型为int32。将信源、由HDL模块生成的Simulink模块、搭建的解调模型连接起来,即完成了仿真模型的建立。为了观察数据变化还需要在模型中添加示波器,主要是在信源、解调输出处添加示波器。但是为了方便了解整个过程中的信号变化,在DATA\_OUT、SIN\_WAVE、COS\_WAVE、乘法器输出端、低通滤波器输出端、下采样输出端、量化输出端、串并转换输出端都添加了示波器。整个系统模型如图9所示。

图9 总体仿真模型

其中包含信源、HDL模块、相干解调、量化、串并 转换五个部分以及两个联合仿真按钮。 双击图中左上方的 compile HDL design 按钮编译 HDL 设计,再双击 launch HDL simulator 按钮打开 Modelsim即可开始联合仿真<sup>[9]</sup>。

在 simulation 菜单下选择 start 即开始仿真。

在执行仿真之前,需要定义Simulink仿真环境中的采样时间与Modelsim仿真时间之间的对应方式。在该设计中Simulink的一个采样时间对应Modelsim中10 ns的仿真时间。

在第一次执行仿真命令时,软件会弹提示信息, 点击 ok 即可打开相应配置对话框如图 10 所示。

| Port List         |          |        |      |     |     |        |      |       |

|-------------------|----------|--------|------|-----|-----|--------|------|-------|

| Port Name         | Simulink | Sample | Time | (3) | HDL | Sample | Time | (s)   |

| /qam_top/clk      |          |        |      | 1   |     |        | · ·  | 1e-00 |

| /qam_top/data_in  |          |        |      | 32  |     |        | 3.   | 2e-00 |

| /qam_top/sin_out  |          |        |      | 1   |     |        |      | 1e-00 |

| /qam top/cos out  |          |        |      | 1   |     |        |      | 1e-00 |

| /qam top/data out |          |        |      | 1   |     |        |      | 1e-00 |

图 10 Modelsim 与 Simulink 的信号速率匹配

可以设置Simulink的一个采样时钟,对于Modelsim的10 ns(即一个时钟周期)的仿真时间。除了data\_in数据速率为1/32倍时钟速率外,其他信号的数据速率都等于时钟速率。

运行完仿真即可查看相应的仿真输入输出信息。

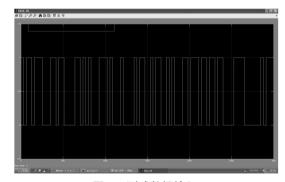

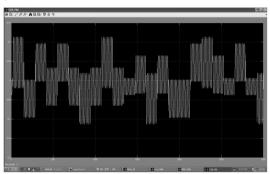

(1)信源输出(即HDL模块的数据输入)如图11 所示。

图 11 测试数据输入

仿真时间为3000个Simulink采样周期,伯努利信源的数据输出速率为32个采样周期输出一次,输出0、1的比例为50%,数据类型为int32(因为在HDL程序中数据输入端口数据类型为integer)。

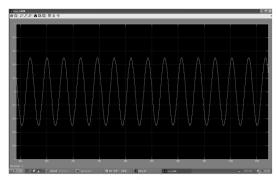

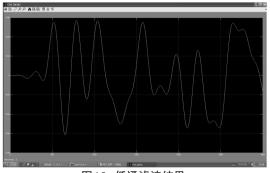

#### (2)同步余弦载波如图12所示。

图中波形为放大后的波形,该载波由 HDL程序 提供,该载波与调制载波共用同一个载波发生器且 具有相同的延迟,因此他们是同频同相的,可以作为 相干解调的本地载波。

图12 同步余弦载波

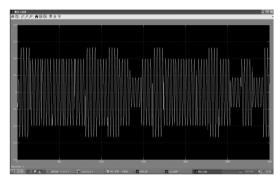

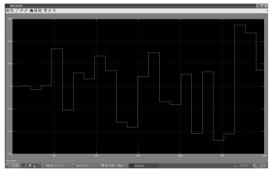

(3)调制后的信号如图13所示。

图 13 调制信号

图中是整个仿真时间的波形,可以方便观察变化情况。该信号为HDL模块调制后的信号,不难发现,经过调制后其相位和幅度均不同原始载波。

(4)调制信号乘以同步余弦载波后的波形如图 14所示。

图 14 调制信号与载波相乘结果

在这个仿真时间下不难发现,在不同时间段信号含有不同的直流分量,该直流分量就是Q路调制的初步解调结果。图中各个近似恒定的部分最窄为128个采样周期,对应一个调制符号的长度。

(5)低通滤波后的信号如图15所示。

由于滤波器的延迟,第一个有效数据出现在480 左右。除去这个偏移量可以近似得到图14所示波形 的一个包络,即可得到图 14 中各个时间段的直流信息。

图 15 低通滤波结果

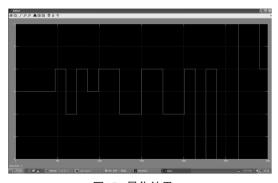

(6)采样保持后的波形如图16所示。

图 16 采样得到波形

采样保持周期为128个Simulink采样周期。由于后续的量化步骤不能直接使用低通滤波得到的信号,所以需要通过采样保持获得适合量化操作的信号。

(7)量化后的波形如图17所示。

图17 量化结果

比较图 16和图 17易发现,信号的幅度发生了变化。图 16中信号幅度最大值也不到 0.5,而且他们基本不相等,图 17中信号值只能为±1、±3。

(8)Q路信息如图18所示。

对量化后的十进制信号转变为二进制信号即可

得到上图。其最短持续时间明显变短,这与输入数据的数据速率是一致的<sup>[10]</sup>。

图18 0路信息

(9)完整的解调数据输出如图19所示。

图 19 完整的解调结果

得到该结果后即可与信源进行对比,如果与信源输出一致则证明调制程序是功能正确的。

## 4 结 论

Matlab/Simulink 与 Modelsim 之间的接口进行仿真可以由 Simulink 模型来生成激励信号,减少了人工

书写测试代码的工作。由于Simulink可以方便地搭建各种模型实现特定的算法,利用该特点可以方便地搭建起HDL算法中的逆向算法模型。如果能够得到与输入端一致的结果,那么就可以证明HDL程序的算法与预期一致。这样有利于提高验证效率,减少了人为失误在验证过程中的影响。

#### 参考文献

- [1] 夏字闻, 胡燕祥, 等. Verilog HDL 数字设计与综合[M]. 2 版. 北京: 电子工业出版社, 2007.

- [2] EDA 先锋工作室, 王诚, 吴继华, 范丽珍, 等. Ahera HbA / CPLD设计(基础篇)[M]. 北京: 人民邮电出版社, 2007.

- [3] 栗芬环. Matlab 和 Modelsim 数字前端设计、仿真验证平台 [C]// 2009.

- [4] 夏宇闻.Verilog 数字系统设计教程[M]. 北京:北京航空航天大学出版社,2008.

- [5] 王一海. 基于 MATLAB 和 ModelSim 的软件无线电课程实验设计[J]. 2011,30(2).

- [6] IEEE Std 1588–2008. IEEE Standard for a Precision Clock Synchronization Pro to col for Networked Measurement and Control Systems[S]. 2008.

- [7] 颜运强,吕高焕. VHDL元件的 Simulink/Modelsim 功能测 试方法[J]. 2009.

- [8] 胡军强,李津生,洪佩琳. 基于 Modelsim FLI 接口的 FPGA 仿真技术[J]. 2002.

- [9] 王诚,薛小刚,钟信潮. XILINX ISE使用详解[M]. 北京:人 民邮电出版社,2005.

- [10] 刘皖,何道君,谭明.FPGA设计与应用[M]. 北京:清华大学出版社,2006.

#### (上接第73页)

算放大器在交流和直流电压的驱动下对驱动电路加载低频调制信号,降低非线性失真;利用三极管的频带及开关特性对激光器加载高频开关调制信号,使激光器能够在不同调制信号下工作,达到对激光器的调制目的。经过试验验证反馈电阻的反馈电流漂移在0.1 mA左右,达到了很好的调整目的。

#### 参考文献

- [1] 黄德修.半导体激光器及其应用[M]. 北京:国防工业出版 社,1999.

- [2] 闫战强,梁勇.一种小功率高稳定半导体激光器可调驱动电源[J]. 激光与红外,2007,37(11):1178-1180.

- [3] 刘澄.半导体激光器稳功率脉冲电源设计[J]. 半导体光电, 2004,25(3):235-237.

- [4] 肖慧荣,邹文栋,伏燕军.大功率半导体激光驱动电源的研制[J]. 激光杂志,2005,26(4):38-39.

- [5] 陈伟,蔡迎波,孙峰.大功率半导体激光器驱动电源保护电路设计[J]. 光学与光电技术,2008,6(6):68-74.

- [6] 汪雨玲.恒流源系统实验研究与设计[D]. 长春:吉林大学, 2006.

- [7] 刘芸,焦明星.半导体激光器用电流源的设计[J]. 应用光学, 2005,26(3).

- [8] FOX R, WAL TMAN, S HOLLBERGL, et al. Precision spectroscopy, diode lasers, and optical frequency measurement technology[M]. Washington: Government Printing Office, 1998.

- [9] Marc Thompson , Martin Schlecht. High power laser diode driver based on power converter technology[J]. IEEE TRANS-ACTION ON POWER ELECTRONICS, 1997.